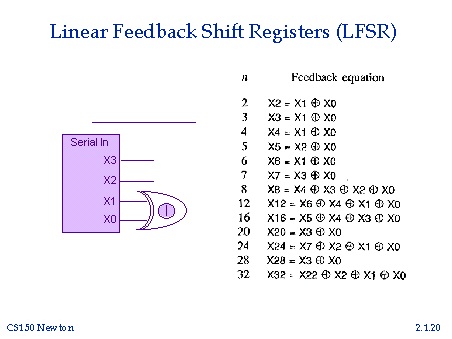

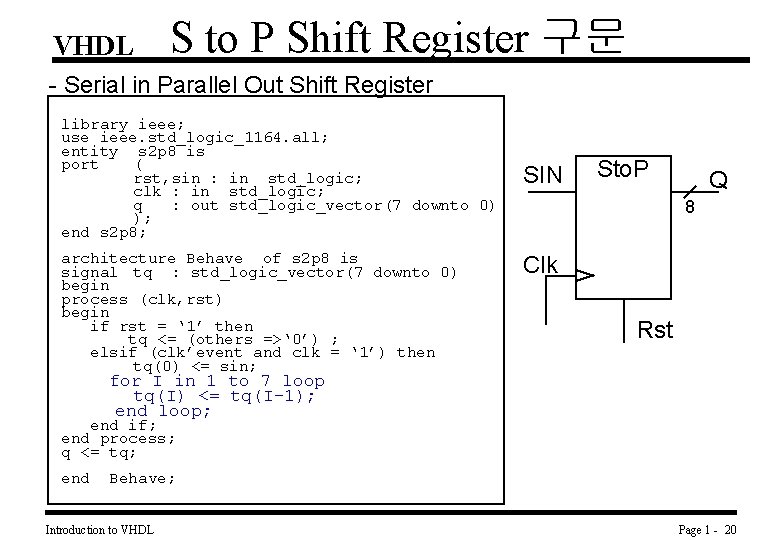

LFSR registers are declared as stdlogicvector signals, and are implemented with the feedback path input the the right-hand side of the register after a left shift. While it will simulate successfully using clock 1 as an if statement condition detecting the rising edge of clock, the convention. VHDL LFSR Package Package of simple functions and procedures to implement any Linear Feedback Shift Register between 3 and 168 bits. Theres also a couple of synthesis gotchas in your code. You could also note that with VHDL -2008 you could evaluate O and wouldnt need temp. 4 bit by 4 bit design with shift registers Linear Feedback Shift Register for. The math involved in analyzing the properties of a LFSR uses Galois fields:Ī simple simulation of a LFSR with two taps: lfsrsim.zipĪ complete list of all dual tap LSFRs up to 42 bit in length and their periods: lfsrperiods. So you want temp to be a variable declared in the process statement. 4 Bit Shift Registers Tutorial with VHDL - YouTube Shift Register in FPGA.

If you need a counter and it does not have to count in a linear way then a LFSR is faster and requires less hardware resources. Only some combinations of taps and lengths will generate a sequence with a period of 2 n-1 cycles. in 2017 Authors designed multibit LFSR based PRNGs circuit using VHDL. There are many possible configurations, the one presented here is very simple and has the property that it will start from an input of all 0's and is very easy to implement in software and hardware.Ī LFSR of this type will never contain only 1's and would stall if loaded with that value. A linear feedback shift register (LFSR) is a shift register whose input bit.

A LFSR (linear feedback shift register) is a shift register where the input is a linear function of two or more bits (taps).

0 kommentar(er)

0 kommentar(er)